-

High-NA EUV 비용 분석 -SPIE (25.4.19)TechStock&Review/SemiConduct 2025. 4. 19. 21:46

Introduction

트럼프 대통령의 말에 따르면 TSMC가 "세계에서 가장 중요한 기업"이라면, EUV 리소그래피 장비는 분명 "세계에서 가장 중요한 기계"일 것입니다. 그렇다면 SPIE Advanced Lithography & Patterning이 세계에서 가장 중요한 컨퍼런스일까요? 꼭 그런 것은 아니지만, 적어도 EUV와 첨단 로직 분야의 최신 진전을 확인할 수 있는 좋은 기회입니다.

출처: imec

이 보고서에서는 올해 SPIE 컨퍼런스에서 발표된 주요 기술 내용과 시장 시사점을 다룹니다. 실제 웨이퍼 생산량이 고객사(인텔) 장비에서 처리됨에 따라 High-NA 가 주요 주제였습니다. 패턴 형성 AMAT Sculpta (Centura Sculpta Pattern-Shaping System) 및 TEL Acrevia 및 directed self-assembly 과 같은 보완적 패터닝 기술이 주목을 받고 있습니다. ASML은 이미 다음 주제인 CFET 시대의 Hyper-NA (2030년 1nm 공정 적용 완료 목표 초기개발 진행중) 에 집중하고 있습니다.Manufacturing Readiness of High-NA EUV - High-NA EUA 제조 준비

인텔의 Steve Carson은 완전히 설치된 두 대의 High-NA EUV 장비의 제조 준비 상태에 대해 주요 기조연설을 진행했습니다. 요약하자면, High-NA EUV에 모든 역량을 집중하여 1년여 전에 첫 번째 장비인 EXE:5000을 설치했고, 그 직후 두 번째 장비를 도입하여 경쟁사보다 앞서 초기 학습을 진행했습니다.

📌 삼성전자는 25년 3월초에 High-NA 장비 EXE:5000 반입하여 설치 및 테스트 진행중

인텔은 14A 노드 출시를 위한 제품 전략의 핵심으로 High-NA EUV를 분명히 보고 있지만, low-NA EUV로도 14A 공정이 가능 하다고 밝혔습니다. 현재 두 대의 완전 설치된 장비에서 총 3만 장의 웨이퍼를 생산하고 있는 인텔은 제조 환경에서 새로운 스캐너의 실현 가능성을 평가할 수 있는 최적의 위치에 있습니다. 인텔의 목표는 low-NA EUV의 문제점이었던 느린 생산 증가를 피하면서, 새로운 High-NA EUV 시스템을 탑재한 개발 파일럿 라인을 기록적인 시간 내에 가동하는 것이었습니다.

출처: 인텔

인텔과 ASML은 새로운 스캐너 기술을 위한 몇 가지 독창적인 제품을 개발했습니다. 일반적인 스캐너 제작 과정은 ASML 벨트호벤 공장에서 조립하는 것입니다. 완전히 조립된 툴은 고객과 ASML이 합의한 사양에 따라 테스트됩니다. 그런 다음 기계는 분해되어 고객사 공장으로 배송되어 설치 및 재조립됩니다. 첫 번째 high-NA 툴의 경우, 공장 통합 및 테스트는 생략되었습니다. 대신, 첫 번째 완전 조립 툴 테스트는 인텔에서 직접 진행되었습니다.

이는 이전에는 시도된 적이 없으며, 새로운 스캐너 기술의 첫 번째 툴/장비(unit)에서는 전례가 없는 일이며 High-NA 스캐너는 low-NA 스캐너와 근본적으로 다르게 ASML과 인텔은 이 과정에서 긴밀히 협력했는데, 이는 툴을 개발하고 신뢰성을 높이는 절차와 방법을 처음으로 익히는 과정이었습니다.📌 반도체 제조회사와 반도체 장비회사가 긴밀히 연계될 수 밖에 없는 업계의 현실을 반영, 예: SK하이닉스 - 한미반도체

하지만 기능적인 스캐너만으로는 고개방(NA) 퍼즐의 일부에 불과합니다. 파일럿 라인은 14A라는 촉박한 일정에 맞춰 공정, 레티클(마스크), 그리고 광학 근접 보정(Optical Proximity Correction / OPC)을 준비해야 했습니다. 특히 네 가지 요소가 모두 상호 의존적이어서 개발이 순차적으로 진행되어야 하기 때문에 이는 매우 어려운 과제였습니다. 바로 이 부분에서 인텔은 혁신과 병렬화를 최대한 강화해야 했습니다.

공정 부분에는 포토레지스트가 포함되는데, 인텔은 low-NA NXE 시스템과 Berkeley의 Microfield Exposure Tool 을 모두 사용하여

high-NA 에 사용할 포토레지스트의 특성을 분석하고 다운셀렉션(down-selection)했습니다. 레지스트에서 패턴을 하부 재료 스택으로 전사하는 식각 공정 또한 일반적으로 이 시점에서 결정됩니다.📌 Berkeley의 Microfield Exposure Tool

전자빔을 사용하여 마이크로 및 나노 크기의 패턴을 웨이퍼 위에 직접 그리는 장비입니다.

- 광 리소그래피(optical lithography)와 달리, 마스크 없이 직접 쓰기(direct write)가 가능.

- 일반적으로 연구 개발용, 특히 최첨단 반도체 공정 연구에 사용됨.

- 차세대 리소그래피 기술 (Next Generation Lithography, NGL)의 실험 플랫폼으로 활용.

- Microfield라는 이름은, 작은 필드에 매우 정밀하게 패턴을 형성할 수 있다는 뜻.

- 일반적인 대면적 노광(wafer scale)이 아닌, 고해상도 소영역 노광이 목적.

OPC는 칩 설계를 리소그래피 마스크에서 복잡한 형상으로 변환하는 데 사용되는 복잡한 소프트웨어 제품군입니다. 일반적으로 OPC 모델은 실제 스캐너와 POR(Process of Record) 레지스트 및 에칭을 사용하여 보정하여 실제 웨이퍼를 인쇄합니다. "키워드"라고도 하는 디바이스 마스크용 OPC 모델은 많은 공정 세부 정보를 필요로 합니다. 이 모델에는 에칭(etch) 바이어스 테이블이 포함되어 있으므로, 에칭(etch) 공정을 먼저 개발하고 특성화해야 합니다. 새로운 스캐너에 고유한 특정 pupil 에 대한 thru-pitch 바이어스도 새로운 레지스트에 대해 특성화됩니다.

하지만 당시에는 high-NA 스캐너를 사용할 수 없었습니다. 그래서 인텔은 실제 웨이퍼 데이터 없이 OPC 모델을 보정하는 새로운 방법을 개발했습니다. 대신, 시뮬레이션과 low-NA 노출을 조합하여 외삽법(extrapolate)을 통해 high-NA OPC 모델을 조정했습니다. 웨이퍼 데이터 보정 (calibration) 없이는 OPC 모델의 정확도가 떨어지기 때문에 일반적으로 이러한 방식을 사용하지 않지만, 인텔은 이것이 가능하다는 것을 증명했습니다.

출처: 인텔

OPC 모델은 low-NA 레티클 대비 더 작은 features와 새로운 anamorphic 셋업을 갖춘 high-NA 레티클을 제작하는 데 필수적이었습니다. OPC 가 중요 경로에서 제외됨에 따라, 스캐너 적격성 평가를 통과하고 파일럿 라인을 거의 즉시 가동할 수 있도록 레티클을 적시에 생산할 수 있었습니다. 전통적으로 이 과정은 스캐너 승인 후 수개월이 소요되었지만, 인텔과 ASML은 이 과정을 거의 0에 가깝게 단축했습니다. 새로운 스캐너 기술을 이렇게 짧은 시간 내에 출시하는 것은 전례 없는 일입니다.High-NA Imaging Results

스캐너가 설치되고 마스크가 확보되자 인텔은 툴의 특징을 파악할 수 있었습니다. 소스 전력과 신뢰성의 기본 지표는 새로운 스캐너 시스템의 목표를 크게 초과했습니다. 소스 전력은 목표의 110%에 달했는데, 이는 새로운 EUV 시스템이 초기 목표를 초과 달성한 최초의 사례입니다. 비교를 위해 NXE:3300 개발 툴은 첫 출하 시 목표 소스 전력의 15%에 불과했고, NXE:3400B 생산 시스템은 목표 소스 전력의 50%를 달성했습니다. ASML은 실제로 소스 로드맵을 앞서 나갔습니다. 신뢰성은 85%로, 개발 당시 이전 시스템보다 훨씬 우수했습니다.

오버레이 성능은 인상적이었습니다. low-NA의 툴에 0.6nm로 정렬되었습니다. 여러 툴에 걸친 이러한 탁월한 성능은 흔히 당연하게 여겨지지만, ASML을 독보적인 기업으로 만드는 요소 중 하나입니다. 이는 칩 제조업체들이 핵심 레이어를 동일한 툴이나 동일한 웨이퍼 척에 국한하지 않고도 우수한 결과를 얻을 수 있도록 툴셋을 자유롭게 조합할 수 있도록 합니다. 경쟁사들은 이 부분에서 수 마일(나노미터)이나 뒤처져 있습니다.

이 오버레이 결과는 인텔과 ASML이 high-NA가 스티칭된 필드에 페널티를 주지 않는다고 선언하기에 충분했습니다. high-NA 광학 소자는 필드 크기를 제한하기 때문에 GPU와 같은 대형 다이에는 스티칭이 필요하기 때문에 이는 큰 우려 사항이었습니다. 이러한 선언에도 불구하고, 팹리스 고객들이 스티칭된 다이를 수용할지는 여전히 미지수입니다. 적어도 스티칭 영역에서는 설계 규칙 제한이 있을 가능성이 높습니다.

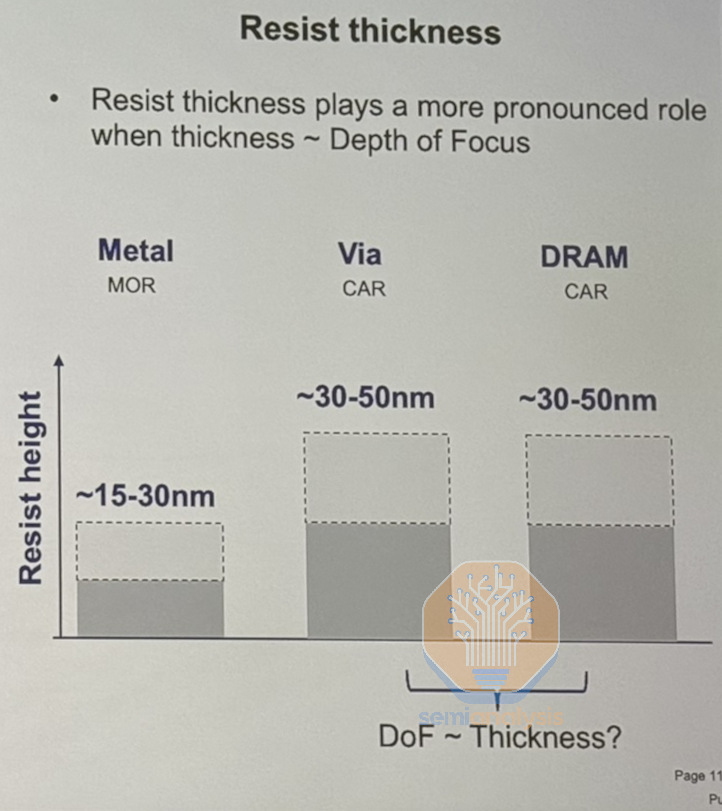

포토레지스트 두께에 대한 컨센서스는 high-NA 리소그래피가 훨씬 얇은 필름 코팅을 필요로 하며, 이는 필요한 광학 초점 심도에 영향을 미친다는 것입니다. 인텔은 제조 가능성에 영향을 미치는 이 중요한 공정 매개변수를 평가할 수 있었습니다. 새로운 high-NA 장비의 초점 제어 성능은 목표 사양을 충족하는 low-NA NXE 시스템보다 우수했습니다.

인텔은 핵심 리소그래피 성능과 함께 금속 및 콘택홀 (contact hole/CH) 층에 대한 초기 소자 데이터를 공유했습니다. 두 층 모두 14A 공정에서 high-NA EUV가 수율의 척도를 바꿀 수 있는 핵심 층입니다. 금속의 경우, 세 번의 low-NA EUV 노광과 총 40개 이상의 공정 단계로 구성된 기존 금속화 방식을 단일 high-NA 노광으로 대체하여 비교했습니다.

low-NA 공정은 pitch 분할과 self-aligned double patterning(SADP)을 사용하여 low-NA EUV 단일 노광 한계를 넘어 크기를 줄인다는 점에 유의해야 합니다. 인텔은 이를 self-aligned litho-etch litho-etch(SALELE)이라고 합니다. SADP는 ALD와 일련의 에칭을 통해 금속 pitch를 원하는 형상으로 분할하기 때문에 많은 공정 단계가 필요합니다. 나머지 두 번의 EUV 노광은 pitch 분할로 인한 라인을 트리밍하고 더 큰 pitch 금속 pitch 를 패터닝하는 컷 마스크에 사용됩니다. high-NA 공정은 이 모든 것을 단일 노광과 훨씬 적은 공정 단계로 대체합니다.

High-NA 단일 노출 SEM 이미지, 패턴 전사 후, 1배 금속 라우팅용. 출처: 인텔

콘택홀(CH) 층의 경우, 인텔은 기존 low-NA multi-patterning(LELE) 공정과 high-NA에서도 유사한 수율을 보이는 수율 데이터를 공유했습니다. 참고로, 층의 상태를 측정하는 데 사용되는 초기 마스크는 유망한 결과를 도출하는 데 매우 저조한 것으로 악명 높습니다. 일반적으로 실시간 수율 신호를 얻으려면 OPC 및 마스크 스핀을 여러 번 반복해야 합니다. 따라서 이 단계에서 high-NA와 기존 공정 간의 수율이 비슷한 것은 매우 인상적입니다.

그들은 low-NA 마스크 단계 수나 전체 공정 단계 수를 공개하지 않았습니다(이에 대해서는 나중에 더 자세히 설명하겠습니다). 저희는 최종 에칭 전사(transfer) 및 금속화(metallization) 전에 low-NA 마스크의 두 패스가 하드 마스크에 저장될 것이라고 가정합니다.

출처: 인텔

마지막으로, 인텔은 새로운 마스크 인프라에 대한 행동 촉구(아래 비용 분석 섹션에서 자세히 설명)와 두 high-NA EUV 시스템 모두 현재 "생산 중"이라는 대담한 선언으로 발표를 마무리했습니다. 이는 high-NA 스캐너가 상용 제품을 가동한다는 것이 아니라, 검증된 공정에서 테스트 웨이퍼를 가동한다는 것을 의미합니다.

여기서 사용된 검증된 공정은 18A일 가능성이 높습니다. 18A는 개발 마지막 단계에 있으며, 잠재 고객에게 마스크 세트를 테이핑 아웃하고 있으며, 공정 단계는 대부분 확정된 상태이기 때문입니다. 이는 하나 이상의 중요 층을 high-NA 로 교체하여 실험하는 데 편리한 기준이 됩니다. 현재 잘 특성화된 18A의 low-NA POR과 비교하면 14A 개발에 대한 귀중한 피드백을 얻을 수 있습니다.

이 개념은 생산 전에 여러 신기술을 테스트하는 데에도 사용됩니다. 7nm 공정의 low-NA EUV의 경우, 비용이 합리적으로 판단되기 전에 수율 학습을 위해 사용되었습니다. 당시 초기 소스 전력이 너무 낮아 EUV가 DUV 쿼드러플 패터닝과 경쟁할 수 없었습니다.High-NA Cost

ASML의 최신 high-NA 시스템인 EXE:5000은 무려 150 metric tons 에 달하는 무게에 비해 가격이 거의 4억 달러에 달합니다. low-NA 시스템보다 가격이 거의 두 배에 달하는 이 시스템은 운영비와 궁극적으로 웨이퍼 비용 증가로 직결됩니다.

https://semianalysis.com/2023/12/11/asml-dilemma-high-na-euv-is-worse/

high-NA vs low-NA 멀티패터닝 보고서에서 논의했듯이, 장비 결정은 비용에 따라 달라집니다. 복잡성을 줄이는 것은 좋지만, 모든 경우에 비용이 더 저렴한 것은 아닙니다. 인텔 발표에서 누락된 부분이 바로 이것입니다. highNA 는 low-NA LELE 또는 SALELE 보다 저렴할까요?

이러한 대안들과 직접적으로 비교되는 지점의 high-NA 실행 경로를 통해 "생산 중"이라는 점을 고려하면, 그들은 답을 알고 있을 것입니다. Intel과 imec, IBM은 모두 14A 노드에서 high-NA를 도입하기 위해 노력하고 있습니다. 그러나 수십억 달러의 비용이 드는 생산 라인 운영을 위한 스캐너를 너무 일찍 도입하는 것은 새로운 지원 기술을 너무 늦게 도입하는 것만큼이나 해로울 수 있습니다.

SPIE 주최측은 가장 중요한 강연을 목요일 오후에 배치하는 경향이 있는데, IBM의 Luciana Meli 가 강연을 했는데, 그녀는 150톤이나 되는 엄청난 규모의 강연 주제인 'high-NA가 비용 효율적인가?'에 대한 유일한 강연을 했습니다.

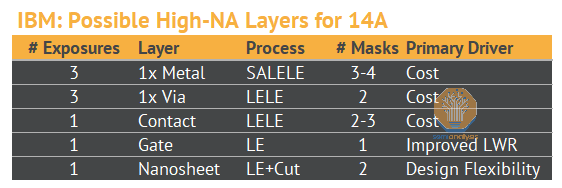

IBM은 벨트호벤 high-NA EUV 연구실에서의 시뮬레이션 및 연구를 바탕으로 몇 가지 주요 결과를 발표했습니다. 먼저, 여러 개의 low-NA 노광을 단일 high-NA 패스로 대체할 경우 가장 큰 잠재적 이점을 얻을 수 있는 14A 층을 파악했습니다.

출처: IBM, SemiAnalysis

비용 분석은 SALELE에 초점을 맞췄습니다. SALELE는 3~4회의 low-NA 노출을 1회의 high-NA 노출로 대체하여 비용 절감 잠재력이 가장 높기 때문입니다. 이 글의 세부 정보는 인텔과의 논의에서 빠진 몇 가지 핵심 사항을 보완합니다. 첫째, SALELE의 공정 단계 수는 high-NA 단일 노출에 필요한 단계 수의 약 두 배입니다. 인텔은 SALELE가 3개 마스크 공정에서 약 40단계로 구성된다고 밝혔기 때문에 high-NA 모듈의 단계 수는 여전히 상당합니다. 비용 측면에서 IBM은 4개 마스크 SALELE 공정이 단일 high-NA 패스보다 1.7~2.1배 더 높다고 주장합니다. 놀라운 결과는 아니지만 비용에 대한 좋은 데이터 포인트입니다. high-NA 단일 노출은 3회 또는 4회 low-NA 노출보다 저렴할 것으로 예상되었습니다.

하지만 IBM은 high-NA 대비 low-NA 이중 패터닝 모델링을 확인하는 데 도움을 주었으며, low-NA 옵션이 더 저렴함을 시사했습니다. IBM의 데이터에 따르면 high-NA 단일 노출 비용은 low-NA 단일 노출 비용의 약 2.5배입니다. 이는 low-NA 마스크 세 개를 high-NA 마스크 하나로 줄이지 않는 한 high-NA에 대한 패스당 비용(CPC) 이점이 나타나지 않음을 강력하게 시사합니다.

IBM 발표에서 또 다른 흥미로운 발견은 금속 공정에서 high-NA의 단일 노광이 금속 팁-팁 설계 목표를 달성하는 데 어려움을 겪을 수 있다는 점입니다. tip-to-tip 형상을 정의하는 전용 절단 마스크를 사용하는 저개구수 SALELE 공정은 이 부분에서 탁월한 성능을 발휘합니다. IBM은 이러한 단점을 보완하기 위해 Applied Materials Sculpta 툴과 같은 방향성 에칭 공정 기술이 필요할 것이라고 제안합니다. 패턴 형성에 대한 자세한 내용은 몇 가지 섹션에서 다루겠습니다.📌 Metal Tip-to-Tip Design이란?

Tip-to-Tip은 말 그대로 **금속 배선의 끝(tip)**이 다른 배선의 끝과 얼마나 가까이 배치되는지를 제어하는 설계 규칙

Metal1 ─────────┐ ┌───────── Metal1

│ │

▼ ▼

(Tip) (Tip)

→ 이 두 "Tip" 사이의 거리 = Tip-to-Tip spacingHigh-NA 6 x 12” Mask

인텔의 전체 회의 발표 마지막 슬라이드에는 대형 high-NA 마스크에 대한 행동 촉구가 포함되었습니다. 인텔은 오랫동안 이 주장을 펼쳐 왔지만, 그럴 만한 이유가 있습니다. 오랫동안 업계 표준이었던 6 x 6인치의 두 배인 6 x 12인치 마스크를 사용하면 스캐너 생산이23~50% 향상될 것이기 때문입니다.

6 x 12인치 마스크는 처리량을 향상시키고 high-NA 필드 스티칭 문제를 해결합니다. 출처: 인텔

전체 필드 노출이 가능하여 스티칭 문제를 해결하고 처리량도 향상됩니다. 스캐너 비용이 상당히 증가한다고 가정할 때, 이는 핵심 레이어의 경제성을 high-NA 에 유리하게 만들 것입니다.

생산성 향상 및 비용 절감을 위한 고개방형 마스크에 대한 인텔의 행동 촉구. 출처: 인텔

인텔을 비롯한 여러 업체들은 마스크 생태계에서 대형 마스크에 대한 큰 장애물은 없다고 말하지만, 전환점은 ASML에 달려 있습니다. 작년 SPIE EUV에서 Christophe Fouquet CEO가 총회에서 대형 마스크에 대해 긍정적으로 언급했지만, 로드맵에는 포함되지 않았고 ASML 측에서도 해당 기술을 개발할 수 있거나 개발할 계획이라고 공식적으로 밝히지 않았습니다. 올해 ASML의 총회 발표는 한 걸음 더 나아가, 더 큰 "생태계가 발전하고 있으며", "영향 연구가 진행 중"이며, "향후 10년 초"에 도입될 가능성이 있다고 밝혔습니다.

ASML은 대형 마스크의 가능성을 인정했습니다. 출처: ASML

이는 사소한 변화가 아닙니다. 6 x 6인치 마스크 크기는 1980년대 프로젝션 리소그래피가 시작된 이래로 표준이었습니다. 블랭크 제조, 레지스트 코팅, 전자빔 묘화, 마스크 세척, 팹 핸들링 등 모든 툴링이 새로운 마스크 크기에 맞춰 재구축되어야 합니다. 이는 200mm 웨이퍼에서 300mm 웨이퍼로 전환하는 것과 같습니다(10년 전 450mm로의 전환 시도가 실패했던 것을 기억하세요). 14A 노드로의 전환 시기는 분명 10년을 훨씬 넘어섰습니다.📌 Blank Manufacturing이란?

Blank manufacturing은 포토마스크(blank mask)의 원재료인 "마스크 블랭크(mask blank)"를 제조하는 공정을 의미합니다. 이 마스크 블랭크는 아직 회로 패턴이 형성되지 않은 상태의 투명 기판으로, 이후에 회로 패턴이 그려져서 반도체 노광 공정에 사용됩니다.

ASML의 경우, 6×12인치 마스크는 NXE, EXE, 그리고 향후 hyper-NA 시스템을 공통 플랫폼에서 제작하여 생산 효율을 높이고자 하는 핵심 EUV 시스템 전략과 상충됩니다. 레티클 스테이지와 핸들링 시스템도 그중 하나입니다. 대형 마스크는 이러한 모듈에 상당한 변경을 요구하여 공통성을 저해할 가능성이 높습니다.

향후 EUV 스캐너는 공통 플랫폼으로 전환될 예정입니다. 출처: ASML

대형 마스크는 ASML의 경제적 이익에 직접적으로 부합하지 않습니다. 일반 마스크 high-NA 스캐너 두 대와 대형 마스크 장비 한 대 중 하나를 선택해야 한다면, 완성된 스캐너 두 대를 판매하는 것이 ASML의 매출에 2억~3억 달러 더 큰 영향을 미칠 것으로 예상됩니다. 대형 마스크 장비를 개발하는 것은 매우 고객 친화적인 방안이 될 것입니다.High-NA EUV: Insertion at 14A or 10A?

14A 공정에서 high-NA는 인텔 공정에서 마스크 세 개를 대체할 수 있는 몇몇 금속층에서만 비용 이점을 제공합니다. TSMC가 A14 공정에서 반드시 3중 EUV 노광을 사용하는 것은 아니며, 이는 인텔에만 국한된다는 점에 유의해야 합니다. 인텔은 다른 층에서는 설계 유연성과 공정 간소화를 제공하는데, 이는 비용과는 무관한 이점이라고 설명합니다.

단 세 개의 레이어만으로 비용을 절감하는 것이 신기술을 조기에 도입하는 위험을 감수할 만한 가치가 있을까요? 비용 절감은 실제로 이루어지지만, 전체 칩 공정(약 100개 레이어) 대비 비중으로 보면 미미합니다. 인텔은 특히 고객이 요구한다면 high-NA 없이도 14A 공정이 가능하다고 공개적으로 밝혔습니다 . 하지만 현재까지의 정황은 인텔이 14A의 핵심 레이어에 high-NA를 도입할 가능성을 시사하고 있습니다. 인텔의 관성은 지금 와서 방향을 바꾸기에는 너무 강할 것입니다. 그리고 6 x 12인치 마스크가 잠재적인 10A 공정에 적합하게 되어 경제성이 매우 높아진다면, 인텔은 조기 도입을 통해 잠재적으로 이득을 볼 수 있을 것입니다. 현재 인텔의 high-Na에 대한 경험과 전문성은 경쟁사보다 훨씬 앞서 있습니다.Metal Oxide Resist

금속산화물 레지스트(Metal Oxide Resist, MOR)은 지난 몇 년 동안 차세대 EUV 포토레지스트 플랫폼으로 주목을 받아 왔습니다. MOR 레지스트는 기존 유기 화학 증폭 레지스트(chemically amplified resists, CAR)에 비해 훨씬 뛰어난 분해능-선폭-감도(line width roughness, RLS) 성능을 제공합니다. EUV는 광자 제한적이기 때문에 감도와 선폭 거칠기(CD) 분산이 특히 중요합니다. 13.5nm 파장에서는 광원에서 방출되는 광자가 상대적으로 적지만, DUV 파장에 비해 훨씬 높은 출력을 냅니다. 선량 감도의 작은 개선은 처리량과 결과적으로 운영 비용에 큰 영향을 미칠 수 있습니다.

하지만 모든 신기술과 마찬가지로, 포토레지스트 플랫폼 변경은 업계 전반의 도입을 촉진하기 위해 상당한 추진력이 필요합니다. 기존 노드의 경우, 그 이점이 변경을 유도할 만큼 크지 않았습니다.

포토레지스트 성능에 대한 RLS 트레이드오프 개념. 출처: Lawson 외. 리소그래피 재료 및 공정 개요

high-NA의 도입으로 마침내 MOR 시대가 도래한 것 같습니다. 초점 길이 (depth of focus, DoF) 또한 NA의 제곱에 비례하여 감소하기 때문에 주요 요인 중 하나입니다. 즉, high-NA 스캐너는 초점 길이가 매우 짧습니다. DoF는 illumination pupil 의 영향도 받는데, 최상의 이미지를 얻으려면 특정 패턴에 맞춰 illumination pupil을 최적화해야 합니다. 안타깝게도, 점점 더 작아지는 패턴에 적합한 pupil은 DoF를 줄이는 경우가 많습니다. 렌즈 NA와 illumination pupil 이 모두 초점 심도를 감소시키면 매우 얇은 포토레지스트 필름이 불가피하게 되는 임계점을 초래합니다.

레지스트 두께는 DoF보다 얇아야 이미지가 레지스트 전체 높이에 걸쳐 초점이 맞춰집니다. 그렇지 않으면 레지스트에 생성되는 패턴의 품질이 저하됩니다. 바로 이 부분에서 얇은 MOR 레지스트가 얇은 CAR 레지스트보다 뛰어납니다. 기존의 CAR 레지스트 플랫폼은 실리콘 질화물(Si3N4)과 같은 하드 마스크에 패턴을 전사하기 위한 식각을 차단하는 기반으로 유기 아크릴 폴리머 백본(탄소-탄소 사슬)을 사용합니다. 얇은 유기 폴리머 필름은 패턴 전사를 견딜 만큼 충분한 식각 저항성을 가지고 있지 않습니다. 그러나 금속 산화물 레지스트는 대부분의 하드 마스크 필름에 패턴을 전사할 때 훨씬 더 우수한 식각 선택성을 제공합니다. 따라서 MOR 레지스트는 CAR보다 광학 성능과 식각 성능이 모두 뛰어납니다.

DoF 가 감소함에 따라 레지스트 두께가 문제가 됩니다. 출처: ASML

금속층 간 상호연결을 위해 금속으로 채워질 촘촘하게 패턴화된 구멍인 비아를 예로 들면, 교차점은 30nm 피치 범위 어딘가에 있을 것으로 보입니다. 다른 예 에서는 아마도 A10 공정에서 약 두 노드 후에 이 피치로 확장될 것입니다. 이는 high-NA 를 도입하는 것이 경제적 일 때를 대비한 우리의 예상과 일치합니다 . 다시 말해, 금속이나 다른 소수의 핵심 층에는 high-NA 과 동시에 MOR을 적용하는 것이 타당할 것입니다. 올해 high-NA 노출 데이터를 사용한 대부분의 SPIE 논문은 CAR 대신 MOR을 사용했습니다.Wet vs. Dry: Resist Coating

포토레지스트의 미래를 좌우할 추가 연구가 진행 중입니다. MOR 공정에 습식 또는 건식 도포 및 현상 방식을 사용할지 여부가 결정될 것입니다. TEL은 현재 습식 스핀 코팅 도포 및 습식 현상 방식을 모두 표준으로 채택하고 있으며, 공정은 자사의 트랙 장비에서 진행됩니다. 램리서치(Lam Research)는 건식 레지스트 증착 및 식각 후 현상 방식을 통해 핵심 층에서 시장 점유율을 확대하려 하고 있으며, 이 두 가지 공정 모두 기존 리소그래피 셀과는 별도로 램리서치 장비를 사용하고 있습니다.

https://semianalysis.com/2021/11/18/lam-research-tokyo-electron-jsr-battle/

연구 결과에서 승자가 나타나기 시작했습니다. 아래에서는 램(Lam)과 텔(TEL) 중 어느 쪽이 시장 점유율을 확보할 가능성이 높은지 살펴보겠습니다. 또한 저개구율 EUV 비용 절감에 필수적인 차세대 펠리클 기술, 패턴 쉐이핑 및 DSA(다이내믹 스캐닝)와 같은 보완적인 패터닝 기술, 그리고 고개구율의 후속 기술인 hyper-NA 에 대해서도 다룹니다.

원문:

https://semianalysis.com/2025/04/14/spie2025/#manufacturing-readiness-of-high-na-euvHigh-NA is Here (for R&D), EUV Cost, Pattern Shaping Gaining Share, 6×12″ Mask, Metal Oxide & Dry Resist, Hyper-NA

“Lithos Graphein” is back as a guest contributor to this report. Follow him on twitter @lithos_graphein If TSMC is “the most important company in the world,” according to President Trump, then EUV …

semianalysis.com

반응형'TechStock&Review > SemiConduct' 카테고리의 다른 글

반도체 경쟁의 패자, 니콘의 화려한 부활? 제조업의 판도를 바꿀 'NXG 600' 이야기 (25.6.14) (4) 2025.06.14 화웨이 Ascend 칩에 대한 미국의 수출 통제 역사와 영향 분석 (25.5.17) (0) 2025.05.16 무어의 법칙을 뒷받침하는 작은 별의 폭발 (25.3.8) (1) 2025.03.08 반도체 풍운아 - 梁孟松 / Mong-song Liang (25.3.1) (3) 2025.03.01 글로벌 기술 산업, ‘중국 쇼크’에 대비하다: 레가시 칩 시장에서의 중국의 급성장 (5) 2025.02.26