-

imec, 시스템-기술 공동 최적화 접근 방식을 사용한 3D HBM-on-GPU 아키텍처의 열 병목 현상을 완화 (25.12.10)TechStock&Review/SemiConduct 2025. 12. 10. 21:58

Imec mitigates thermal bottleneck in 3D HBM-on-GPU architectures using a system-technology co-optimization approach

2025 IEEE 국제 전자소자 회의(IEDM)에서 첨단 반도체 기술 분야의 세계적인 연구 센터인 imec은 차세대 AI 애플리케이션을 위한 유망한 컴퓨팅 아키텍처인 3D HBM-on-GPU(그래픽 처리 장치 내 고대역폭 메모리)에 대한 최초의 열 시스템-기술 공동 최적화(System-Technology Co-Optimization / STCO) 연구를 발표했습니다. 기술과 시스템 수준의 완화 전략을 결합함으로써, 현실적인 AI 학습 워크로드에서 최대 GPU 온도를 140.7°C에서 70.8°C로 낮출 수 있었으며, 이는 현재 2.5D 통합 옵션과 동일한 수준입니다. 이 결과는 교차 계층 최적화(즉, 모든 추상화 계층의 노브를 공동 최적화)와 광범위한 기술 전문성을 결합하는 것의 강점을 보여주는데, 이는 imec만의 독보적인 조합입니다.

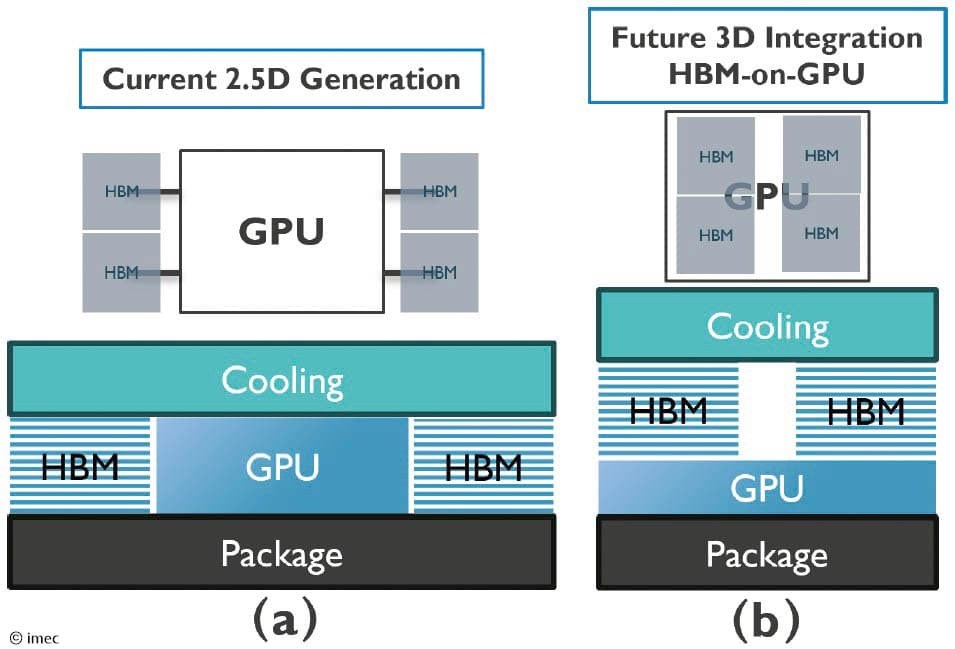

그래픽 처리 장치(GPU) 위에 고대역폭 메모리(HBM) 스택을 직접 통합하는 것은 데이터 집약적인 AI 워크로드를 위한 차세대 컴퓨팅 아키텍처를 구축하는 매력적인 접근 방식을 제공합니다. 이 3D HBM-on-GPU는 실리콘 인터포저 위에 HBM 스택을 (1~2개의) GPU 주변에 배치하는 기존 2.5D 통합 방식과 비교하여 컴퓨팅 밀도(패키지당 4개의 GPU), GPU당 메모리, 그리고 GPU 메모리 대역폭 측면에서 엄청난 발전을 약속합니다. 그러나 이러한 공격적인 3D 통합 방식은 높은 국부 전력 밀도와 수직 열 저항으로 인해 열 문제가 발생하기 쉽습니다.

2025 IEDM에서 imec은 3D HBM-on-GPU 통합에 대한 최초의 포괄적인 열 시뮬레이션 연구를 발표합니다. 이 연구는 열 병목 현상을 파악할 뿐만 아니라 아키텍처의 열적 타당성을 높이기 위한 전략도 제시합니다. imec 연구진은 공동 최적화 기술과 시스템 수준의 열 완화 접근법을 통해 현실적인 AI 학습 워크로드에서 최대 GPU 온도를 141.7°C에서 70.8°C로 낮추는 방법을 보여줍니다.

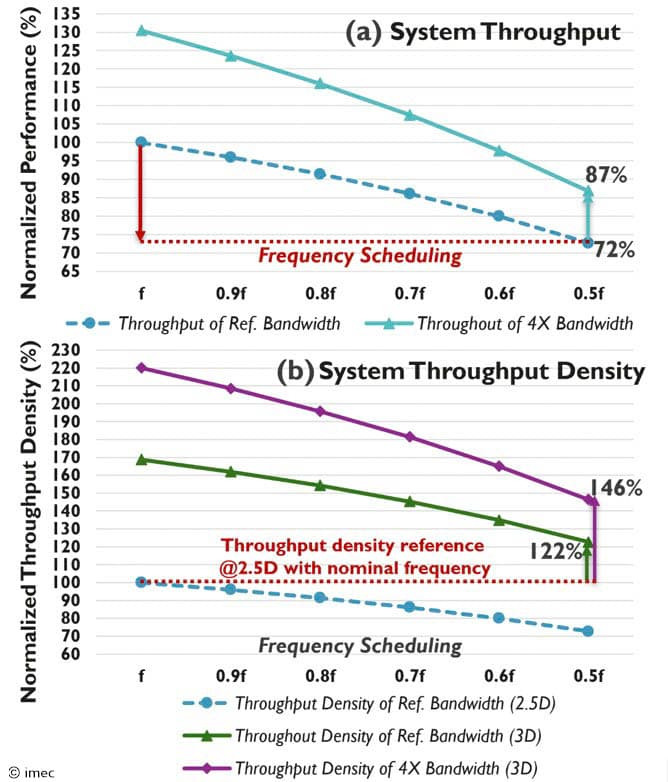

이 모델은 마이크로범프를 사용하여 GPU 바로 위에 12개의 하이브리드 본딩 DRAM 다이로 구성된 4개의 HBM 스택을 배치한다고 가정합니다. HBM 위에 냉각이 제공됩니다. 업계 관련 전력 프로파일에서 도출된 전력 맵을 적용하여 로컬 핫스팟을 식별하고 2.5D 기준선과 비교합니다. 열 완화 전략을 사용하지 않을 경우, 3D 모델은 최대 GPU 온도가 141.7°C로 나타나 GPU와 HBM 작동에 비해 매우 높은 반면, 2.5D 통합 벤치마크는 동일한 냉각 조건에서 최대 69.1°C로 작동 가능한 온도를 나타냅니다. 이 데이터를 시작점으로 사용하여 기술 및 시스템 수준의 열 완화 전략의 공동 영향을 평가했습니다. 기술 수준의 전략에는 HBM 스택 통합 및 열 실리콘 최적화가 포함됩니다. 시스템 수준에서는 양면 냉각과 GPU 클럭 스케일링의 영향을 평가했습니다.

imec의 시스템 기술 프로그램 디렉터인 James Myers는 "GPU 코어 주파수를 절반으로 줄임으로써 최대 온도가 120°C에서 100°C 미만으로 낮아져 메모리 작동의 핵심 목표를 달성했습니다. 이 단계에서는 28%의 워크로드 페널티(즉, AI 학습 단계 속도 저하)가 발생하지만, 3D 구성이 제공하는 높은 처리량 밀도 덕분에 전체 패키지는 2.5D 기준선보다 우수한 성능을 발휘합니다. 현재 이 접근 방식을 사용하여 다른 GPU/HBM 구성(예: HBM 위에 GPU 배치)을 연구하고 있으며, 향후 열 제약 조건을 예상하고 있습니다."라고 말했습니다.

imec 로직 테크놀로지 부사장 Julien Ryckaert는 다음과 같이 말했습니다. "또한 열적으로 더욱 견고한 컴퓨팅 시스템을 구축하는 imec의 교차 기술 공동 최적화(XTCO) 프로그램의 역량을 처음으로 시연합니다. XTCO는 imec의 기술 로드맵을 주요 산업 시스템 확장 과제에 효율적으로 연계하기 위해 2025년에 시작되었으며, 컴퓨팅 밀도, 전력 공급, 열, 메모리 밀도 및 대역폭이라는 네 가지 핵심 시스템 수준 기둥을 기반으로 합니다. STCO/DTCO의 사고방식과 imec의 광범위한 기술 전문성을 결합한 이 특별한 조합은 컴퓨팅 시스템 수요의 성장과 다각화에 대응하는 데 매우 중요한 가치를 지닙니다. 팹리스 및 시스템 기업을 포함한 전체 반도체 생태계 내 기업들이 XTCO 프로그램에 참여하여 중요한 시스템 확장 병목 현상을 공동으로 해결하기를 바랍니다."역자주: HBM base die removal 는 최근 엔비디아, TSMC 가 주도하고자 하는 HBM base die (logic die) 에 Tensor core 와 통신 연산 로직 설계 (엔비디아) 및 제조 (TSMC)의 흐름과 일치한다. 3D 적층으로 인한 열 관리를 위해 Double-sided cooling (당연하게도 액체 냉각일것으로 추정됨)이 추가 되었고 GPU 코어 클럭수 절반으로 단축하는 부분은 성능에 대해서 아쉬운점이 있으나 추론 단계 (Prefill 과 Decoding 단계 분리) 에서는 충분한 성능을 보일 것으로 생각된다.

참조 원문:

반응형'TechStock&Review > SemiConduct' 카테고리의 다른 글

애플과 TSMC: 현대 반도체를 탄생시킨 파트너십 (26.1.10) (1) 2026.01.11 입자가속기 기반 EUV 광원 생성 원리와 기술 특징 (25.12.21) (0) 2025.12.21 ASML 스캐너의 역사 와 중국의 도전 (25.10.24) (1) 2025.10.24 High-NA 판매의 어려움: EUV 멀티패터닝의 관행, Depth of Focus 에 대한 미언급 (25.9.30) (1) 2025.09.30 Huawei Ascend 생산 증가: Die Banks 와 HBM 병목 현상 (25.9.11) (1) 2025.09.11